인텔이 차세대 10나노 공정 기술 스펙을 공개했다. 트랜지스터 집적도 면에서 삼성전자나 TSMC 등 경쟁 업체보다 우월하다는 점을 특히 강조했다.

인텔은 28일(현지시간) 미국 샌프란시스코에서 기술·제조 발표회를 열고 올 하반기 양산 체제에 돌입하는 10나노 공정의 세부 내역을 밝혔다. 인텔 8세대 코어 프로세서가 10나노 공정으로 생산된다. 최첨단 파운드리 서비스를 위한 기술이기도 하다. 삼성전자와 TSMC는 10나노를 넘어 7나노 공정 도입을 서두르고 있다. 그러나 인텔은 '숫자'가 중요한 것이 아니라며 제조 기술 분야에서 여전히 자사가 우위임을 과시했다.

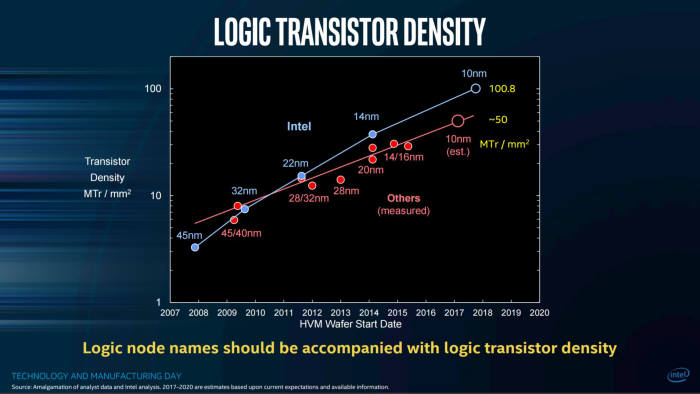

인텔은 트랜지스터 집적도가 경쟁사보다 두 배가량 높다고 강조했다. 인텔 10나노 공정으로 생산된 칩은 1㎟당 1억800만개 트랜지스터가 집적된다. 인텔이 제시한 자료에 따르면 타사(삼성전자나 TSMC) 10나노 칩의 트랜지스터 집적도는 1㎟당 5000만개에 그치는 것으로 추정됐다. 인텔은 게이트와 게이트 전극 형성 방법을 보다 효율적으로 개선한 새로운 '하이퍼스케일' 기술을 도입해 이처럼 높은 집적도를 달성할 수 있었다고 밝혔다. 게이트 핀 높이를 늘리고 거리를 좁힌 것도 성능과 집적도 확대에 기여했다. 동일 트랜지스터 집적도라면 14나노에선 면적이 17.7㎟이던 칩이 10나노 공정에선 57% 줄어든 7.6㎟로 면적을 갖게 된다.

마크 보어 인텔 기술·제조그룹 시니어 펠로는 “일부 기업이 의미 있는 수준으로 집적도를 높이지 못했음에도 20나노에서 14·16나노, 10나노 등으로 노드 이름을 계속 낮춰나가고 있다”면서 “단위 영역당 절대적인 트랜지스터 집적도로 측정을 해야 한다”고 말했다. 이러한 측정 기준을 도입하면 업계 혼란을 줄일 수 있다는 게 그의 설명이다.

인텔은 현재 가동하고 있는 14나노 공정 역시 타사보다 기술적으로 우월하다면서 게이트 간격, 게이트 핀 간격, 로직 셀 높이, 금속배선 간 최소 간격 수치를 모두 공개하기도 했다. 이 같은 수치를 대입해 계산해보면 인텔 14나노 공정으로 생산된 칩의 트랜지스터 집적도는 1㎟당 3750만개로 가장 높다. TSMC 16나노는 1㎟ 2900만개, 삼성전자 14나노는 3050만개였다.

인텔의 2인자로 불리는 스테이시 스미스 제조운영·판매총괄 수석부사장은 “인텔은 공정 기술 분야에서 계속적으로 선두 자리를 놓치지 않고 있다”면서 “이는 앞으로도 계속 유지될 것”이라고 강조했다.

인텔은 45나노 공정에서 고유전율(하이-K) 증착 물질을 덮은 메탈 게이트 기술을 첫 상용화했다. 유전율이 높은 증착 물질을 게이트 위로 증착하면 전류 누설과 간섭 현상을 줄일 수 있다. 경쟁사는 3년 뒤 28나노 공정에 이 기술을 전면 도입했다. 3차원(D) 게이트 형상의 핀펫(FinFET) 기술 역시 인텔이 가장 빠르게 적용했다. 인텔 22나노 칩에 이 기술이 첫 적용됐다. 삼성전자나 TSMC는 3년 뒤인 14·16나노 공정에서야 핀펫 트랜지스터를 첫 도입했다. 인텔 14나노, 10나노에 도입된 하이퍼스케일(면적 효율적인 게이트 형성에 관한 방법론) 기술 역시 경쟁사는 뒤따라오고 있는 형국이다.

업계 관계자는 “공정 기술 분야에서 선두를 유지하고 있다는 인텔의 주장은 빈말이 아니다”라면서 “이번 발표회는 자사 기술 경쟁력을 과시함과 동시에 파운드리 사업을 강화하고자 하는 포석이 깔려있다”고 설명했다.

이날 인텔은 사물인터넷(IoT) 기기에 탑재되는 저전력 반도체를 위한 22나노 핀펫 공정인 '22FFL(FinFET Low Power)' 기술도 발표했다.

한주엽 반도체 전문기자 powerusr@etnews.com