인텔이 차세대 데이터센터용 프로세서의 내부 아키텍처를 일부 공개했다. 프로세서 코어 간 데이터 송수신 구조·방법을 변경해 속도, 효율을 개선한 것으로 나타났다. 이 제품은 조만간 공식 출시된다. 업계에선 인텔의 차세대 데이터센터 프로세서가 시중에 판매되기 시작하면 클라우드와 빅데이터 인프라의 연산 효율이 보다 높아질 것으로 예상하고 있다.

인텔은 20일 차세대 데이터센터용 프로세서 아키텍처 '제온 스케일러블 프로세서(Xeon Scalable Processors)'의 핵심 개선 사항을 공개했다. 제온 스케일러블 프로세서 아키텍처는 개발 코드명 '스카이레이크-SP'로 알려진 차세대 제온 플래티넘, 골드, 실버, 브론즈 제품에 탑재된다.

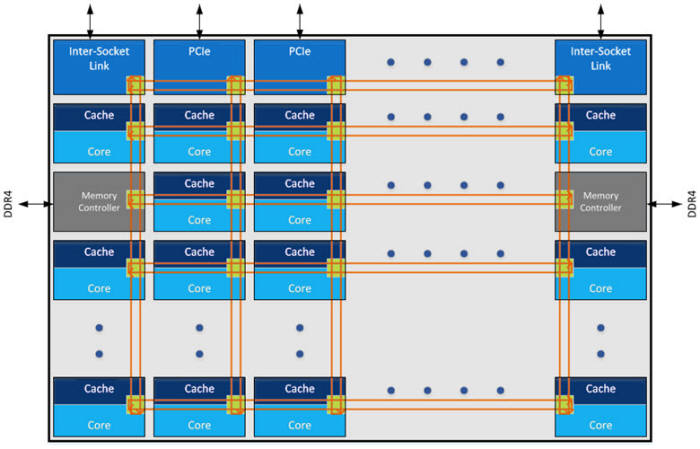

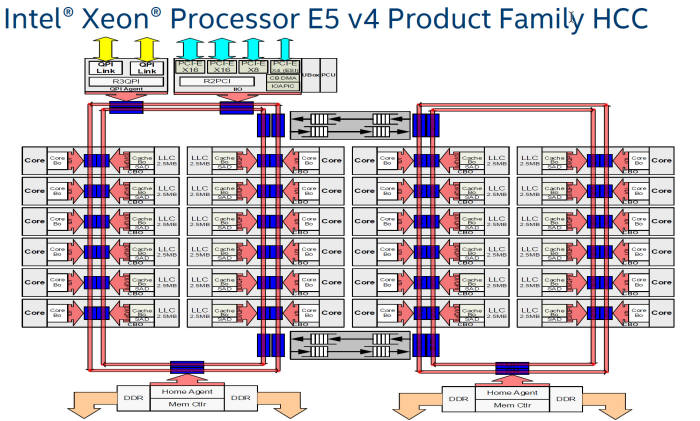

새로운 아키텍처는 코어 간 데이터 송수신 구조를 기존 링(Ring) 방식에서 메시(Mesh) 방식으로 변경했다. 코어 개수가 많은 데이터센터 프로세서에 보다 특화된 구조를 채택했다.

일반 PC 프로세서는 코어 숫자가 4개, 8개 수준에 그친다. 그러나 데이터센터 프로세서에는 보다 많은 중앙처리장치(CPU) 코어와 데이터 임시 저장을 위한 캐시 메모리, 각종 컨트롤러가 탑재된다.

예컨대 기존 고성능 제온 프로세서 시리즈에는 최대 24개 코어가 들어가 있다. 1번부터 12번 코어와, 13번부터 24번 코어가 각각 다른 링 버스로 엮인 구조였다. 첫 번째 링에서 두 번째 링 버스로 데이터를 넘기려면 중앙 버퍼를 거쳐야만 했다. 코어 숫자가 더 많아질 경우 효율성 문제를 야기할 수 있는 구조다.

새로운 제온 스케일러블 프로세서는 이 같은 링 구조를 메시 방식으로 바꿨다. 다(多) 코어를 그물망처럼 촘촘하게 연결했다는 의미에서 '메시'라는 이름을 붙였다. 이 구조를 적용해 데이터 전송 거리가 짧아졌고 지연시간도 낮아졌다고 인텔은 설명했다. 프로세서 설계 관점에선 코어 개수를 늘리는 것도 용이하다.

인텔은 이 같은 프로세서 아키텍처의 구조 개선이 대도시의 교통 체증을 해소하는 방법과 비슷하다고 설명했다.

아킬레시 쿠마르 인텔 스카이레이크-SP CPU 아키텍트는 “메시 아키텍처는 기존 링 방식과 비교해 직접 데이터 도달 경로를 늘리고 병목은 제거함으로써 낮은 동작 주파수와 전압에서도 높은 대역폭과 저 지연시간을 보장한다”면서 “이는 마치 체증 없이 최적 속도로 주행하도록 설계된 고속도로를 설치한 것과 같은 효과”라고 설명했다.

인텔은 조만간 새로운 아키텍처를 적용한 신형 제온 프로세서 제품군을 출시하고 데이터센터 프로세서 시장을 계속 장악해나가겠다는 계획을 세웠다.

한편 AMD도 새로운 젠(Zen) 아키텍처 기반 데이터센터용 프로세서 '에픽(코드명 네이플스)'을 공식 출시할 예정이다. AMD는 한동안 데이터센터 시장에 신제품을 내놓지 못했다. 인텔 신규 제품에 견줘 AMD의 신제품이 어느 정도의 성능 혁신을 이뤘을 지 업계 관심을 모으고 있다.

한주엽 반도체 전문기자 powerusr@etnews.com