세계 최대 파운드리 업체인 대만 TSMC가 올 상반기 극자외선(EUV) 노광장비를 이용한 5나노(㎚) 공정을 시험 가동한다. 7㎚ EUV를 가동한 삼성전자와 TSMC 간 미세 공정 기술 경쟁이 가열되는 양상이다.

25일 시장조사업체 IC인사이츠에 따르면 TSMC는 현재 EUV를 활용한 5㎚ 공정을 개발 중에 있으며, 올 상반기 '위험생산(risk production)'에 들어갈 것으로 알려졌다.

위험생산은 고객사로부터 승인을 받기 전 시범적으로 가동하는 것으로, 양산에 돌입하기 위한 과정의 일환이다. TSMC는 위험생산을 거쳐 2020년 '대량생산(volume production)'을 목표하는 것으로 전해졌다.

TSMC가 성공적으로 5㎚ EUV 공정을 가동하면 세계 최초 타이틀을 거머쥘 전망이다. 차세대 노광장비로 꼽히는 EUV를 업계 최초 도입한 건 삼성전자다. 하지만 삼성의 EUV는 7㎚ 공정이다. 삼성은 작년 10월 시험 가동을 시작했고, 고객사 일정에 맞춰 올 하반기 본격 양산에 들어갈 예정이다. 삼성 7㎚ EUV 고객사는 퀄컴과 IBM으로 알려졌다.

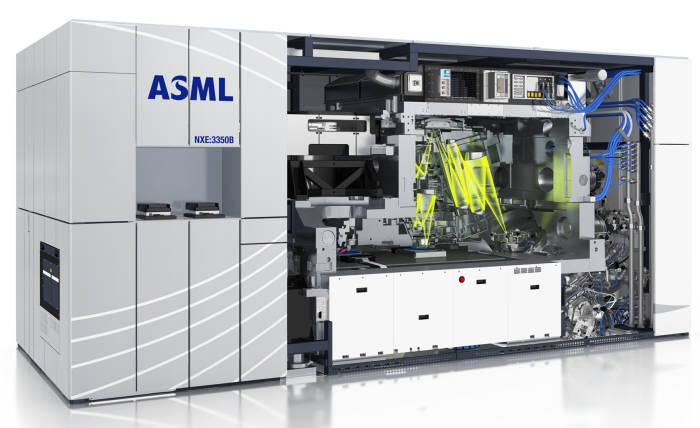

EUV가 중요한 건 미세회로 때문이다. 반도체는 회로가 미세화될수록 성능과 전력 효율이 개선된다. 지금까지 웨이퍼에 반도체 회로를 새기는 작업(노광)에는 불화아르곤(ArF)이 사용돼 왔다. 그러나 반도체 회로가 10㎚ 이하로 설계되면서 기존 노광 공정은 한계에 다다랐고 이에 EUV가 새롭게 고안됐다. EUV는 기존 ArF보다 파장 길이가 14분의 1에 불과하다. 좀 더 세밀한 반도체 회로 패턴 구현에 적합하고 복잡한 멀티 패터닝 공정을 줄일 수 있어 반도체 고성능화와 생산성을 동시에 확보할 수 있는 것으로 평가된다.

TSMC와 삼성은 앞으로도 일진일퇴를 주고받을 것으로 예상된다. 삼성은 2020년까지 3㎚ EUV 공정을 개발할 계획이다. 삼성 파운드리 사업을 총괄하는 정은승 사장은 작년 12월 열린 반도체 학회에서 “3㎚ 공정 성능 검증을 마치고 기술 완성도를 높여가는 중”이라고 밝혔다. 계획대로 개발이 이뤄지면 3㎚에서는 다시 삼성전자가 주도권을 쥘 전망이다.

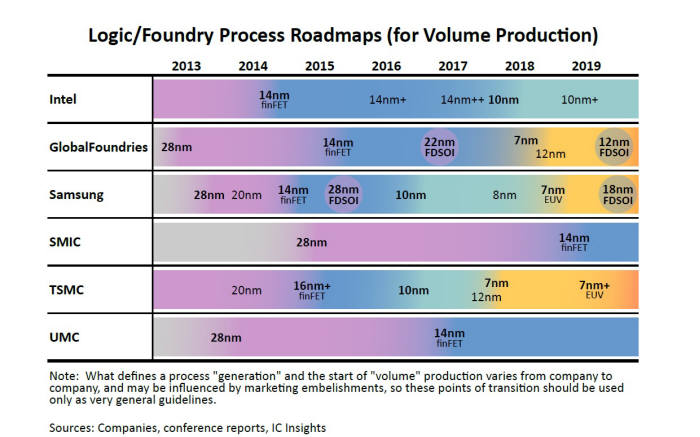

세계 파운드리 시장 규모는 70조원에 이른다. 삼성전자는 세계 최대 메모리 반도체 기업이지만 파운드리 시장에서는 업계 4위다. 삼성은 EUV와 같은 첨단 파운드리 공정 기술로 시장을 탈환하겠다는 의지를 보이고 있다. 세계 2위 파운드리 업체 글로벌파운드리는 7나노 공정 개발을 포기했다. EUV 설비 도입에 막대한 투자가 들고 공정 기술 개발도 어려워서다. 이에 따라 파운드리 미세 공정 싸움은 TSMC와 삼성전자로 압축되는 상황이다.

윤건일 전자/부품 전문기자 benyun@etnews.com