세계적 반도체설계자동화(EDA) 툴 업체 케이던스가 인공지능(AI) 기능을 적극 도입하고 있어 주목된다. 이를 통해 설계 시간을 획기적으로 줄이고 정확도도 올렸다. 삼성전자의 5나노미터(㎚) 이하 초미세 공정 설계에도 활용된다.

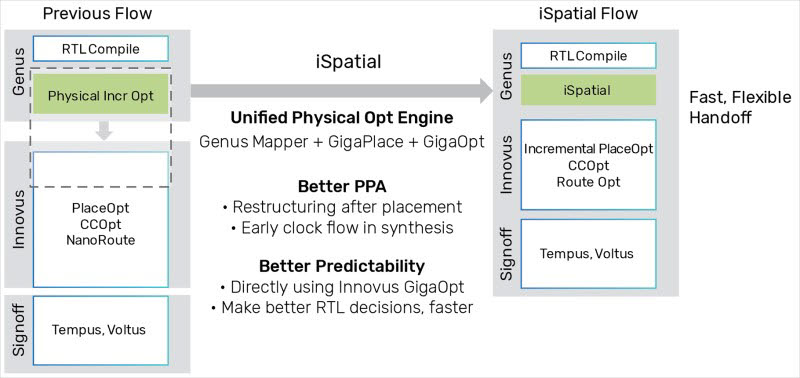

케이던스는 최근 설계 툴에 AI와 머신러닝 기술을 도입한 '아이스패셜(iSpatial)' 기술을 선보였다.

아이스패셜 기술은 반도체 설계 중 많은 시간이 들었던 과정을 획기적으로 줄일수 있다. 기존 설계 툴은 설계 작업 중 결함이 발견됐을 때, 회로의 모든 부분을 바꾸면서 새로운 검증 과정을 거쳐야 했다. 미세한 오류가 발생해도 처음부터 다시 설계를 진행해야 하는 비효율이 발생했다. 그러나 AI 기술이 도입된 케이던스 툴은 특정 회로만 콕 집어서 수정할 수 있다.

설계 정확도를 높일 수 있는 장점도 있다. 설계 초반 단계인 레지스터전송레벨(RTL)에서 조금 더 구체적인 회로 설계인 게이트레벨로 넘어갈 때, 기존에는 설계가 제대로 이뤄졌는지 판단할 수 있는 물리적인 데이터가 없었다. 그러나 아이스패셜 툴은 머신러닝 기술을 활용해 완성된 회로 모양을 예상할 수 있다.

케이던스 관계자는 “AI로 예상한 회로 모양은 80~90% 정확도를 지닌다”며 “설계 초기 과정에서도 오차를 최소화하기 때문에 상당히 매끄러운 작업을 진행할 수 있다”고 전했다.

이 툴은 5㎚ 이하 공정을 활용한 초미세 칩 설계를 지원한다. 칩 디자인 시간을 최대 3분의 1로 단축시킬 수 있고, 칩의 전력·성능·면적(PPA)을 기존 툴을 활용할 때보다 20% 끌어올릴 수 있다는 게 케이던스 설명이다.

케이던스는 아이스패셜 출시 전에도 배선(routing) 설계 작업에 AI 기술이 도입한 사례가 있다. 앞으로 다양한 설계 과정에 AI를 도입해 칩 제조사 생산성을 극대화한다는 방침이다. 삼성전자, 미디어텍 등 세계 주요 반도체 제조사들도 아이스패셜 기술을 활용했다.

박재홍 삼성전자 파운드리사업부 부사장은 “이번 설계 툴로 4나노 공정 디자인 실험을 보다 수월하게 진행할 수 있었다”고 전했다.

강해령기자 kang@etnews.com