반도체와 디스플레이, 배터리를 포함한 첨단 전자부품은 4차 산업혁명 씨앗 산업으로 꼽힌다. 전자부품 산업이 지금보다 진화하지 않으면 4차 산업혁명은 성장동력을 갖추기 어렵다는 데 전문가 대부분이 같은 견해를 갖고 있다.

진화 방향은 부품마다 제각기 다르다. 반도체는 미세화 한계를 극복함과 동시에 인공지능(AI) 구현을 위한 뇌 모방형 제품 개발에 힘을 쏟아야 한다. 디스플레이는 생산 공정과 재료 혁신으로 휘어지거나(플렉시블), 접히거나(폴더블), 늘어나는(스트래처블) 제품과 함께 완전한 투명 제품이 나오는 쪽으로 연구개발(R&D)이 이뤄져야 한다는 분석이다. 배터리는 저장 밀도와 안전성을 높이는 것이 중요 과제다. 한 번 충전으로 수 천 km를 갈 수 있는 전기차, 그리고 이 같은 친환경 기술을 기반으로 한 자율주행차를 개발하기 위해 배터리 밀도와 안전성 향상은 반드시 해결돼야 할 과제다. 이외에 전자부품 기초 소재인 나노 기반 재료 분야 혁신, 센서, 커넥터, 모터 등 주변 부품 산업도 발전해야 한다. 4차 산업혁명을 이루기 위해 첨단 부품 분야가 어떤 방향으로 진화해야 하는지를 살펴봤다.

<1>차세대 반도체

◇AI 구현 칩 개발은 중장기 과제

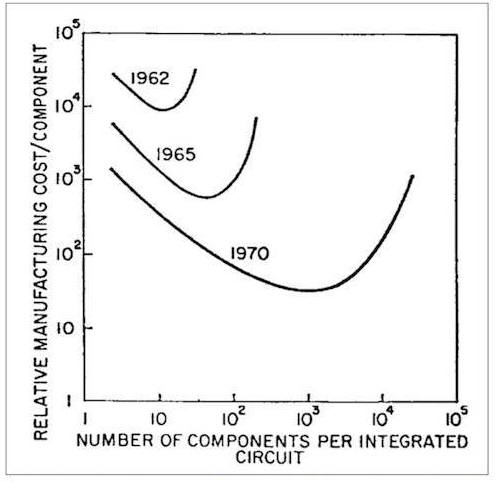

지금까지 반도체 발전 방향은 '미세화'였다. 같은 면적 칩에 보다 많은 트랜지스터를 집적하면 속도는 빨라지고 전력 소모량과 발열은 줄어든다.

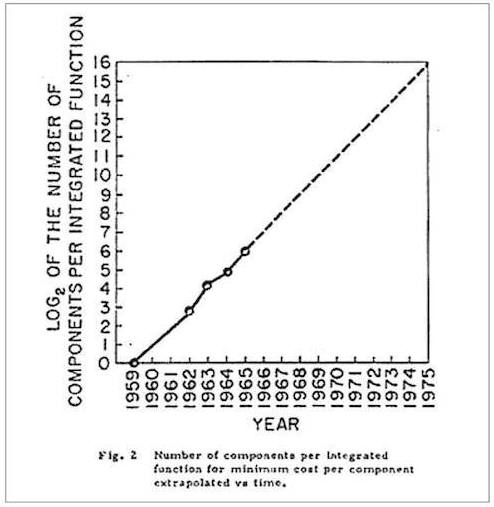

인텔 창업자 고든 무어는 1965년 반도체 집적도가 매 2년마다 두 배씩 증가할 것이라는 이론을 내놓았다. 유명한 '무어의 법칙(이론)'이다. 지난 50여년간 반도체 업계는 이 이론을 지키기 위해 미세화에 많은 힘을 기울여왔다. 자연 법칙이 아닌 그저 유명한 한 공학자 이론을 지키려 했던 이유는 이 방법이 성능은 높이고 전력소모량을 줄이는 이점 외에도 칩 원가를 내릴 수 있는 '경제적' 장점이 컸기 때문이다.

말하자면 일석삼조다. 미세화를 이루면 성능 좋고 전력을 적게 쓰는 칩을 싸게 생산할 수 있었다. 미세화에서 경쟁력을 갖춘 기업은 살아남고, 그렇지 못한 기업은 도태되거나 다른 기업에 팔리거나 망해버렸다.

최근 이 같은 무어의 이론은 한계에 부닥쳤다. 기존 기술로는 회로 선폭을 더 이상 미세화하기가 어렵게 됐다. 미세화를 하려 한다면 어떻게든 할 수는 있지만, 오히려 원가는 올라가기 때문에 무작정 밀어붙이기가 힘들다.

근래 몇 년 사이 이 같은 상황이 계속됐다. PC나 스마트폰에 탑재되는 메인 프로세서를 예로 들면 28나노보다 20나노가, 20나노보다 14나노, 10나노 제품의 초기 생산 원가가 높은 것으로 나타났다. 이 때문에 공정 미세화 주기는 계속 더뎌지고 있다. 이는 반도체가 탑재되는 완성품 성능 향상 속도가 과거 대비 느려진다는 의미다.

4차 산업혁명 시기도 뒤처질 수 밖에 없다. 기술 진화가 계속 정체되면 결국 후발주자에 따라잡힐 수밖에 없다는 우려도 나온다. 이미 중국은 반도체 분야에 천문학적 국가 자금을 쏟아붓는 중이다. 따라서 단기 과제로 10나노 미만 공정까지 끊김없는 미세화를 이루기 위한 생산, 장비, 재료 분야 혁신이 필요하다.

◇전 공정 분야 장비 재료 혁신 필요

반도체는 기초 재료인 원형 웨이퍼 원판 위로 각종 증착 재료를 덮고 회로 패턴을 그리고, 필요 없는 부분을 깎아내고, 찌꺼기를 세정하는 과정의 연속이다. 지금 가장 큰 문제가 되는 것은 회로 패턴을 그리는 노광 공정 분야 장비, 재료, 각종 부분품 기술 병목이다.

현재 첨단 반도체 생산 공정 라인에 도입돼 있는 노광 장비는 빛 파장이 193nm인 불화아르곤(ArF) 엑시머 레이저와 액침(液浸, immersion) 기술을 활용한다. 물리적으로 한 번에 그릴 수 있는 회로 선폭은 38나노에 그친다. 이 때문에 반도체 제조업체는 회로 패턴을 두 번 혹은 세 번에 나눠서 그리는 멀티 패터닝 공정을 활용한다. 이는 공정 횟수 증가를 야기했다. 원가가 올라갔다는 의미다.

네덜란드 노광 장비 전문업체 ASML은 빛 파장이 13.5nm로 10나노 이하 패턴을 한 번에 그릴 수 있는 극자외선(EUV) 노광 장비를 개발하고 있다. 이 장비는 내년부터 양산 라인에 일부 도입될 것으로 예상된다.

EUV 노광 장비에 맞는 포토레지스트(PR)와 검사 장비, 마스크 보호 펠리클 등 주변 부품과 재료, 인프라 개발은 아직이다. PR와 검사 장비는 국내 기술력으로는 어렵다. 여전히 일본과 미국 기술을 들여와서 써야 한다.

하지만 펠리클 분야는 국내 업체나 학계가 한 번 도전해볼 만하다는 것이 전문가 설명이다. 펠리클은 소모품으로 쓰이기 때문에 미세화 한계를 넘어서는 요소 기술로 개발하면 적잖은 수익을 올릴 수 있다.

증착 재료 분야에서는 캐패시터 혹은 전류를 흘리는 게이트에 쓰이는 신재료 개발이 시급하다. D램 캐패시터는 전하를 저장하는 공간이다. 이 곳 전하 저장 유무로 0과 1을 판단한다. 미세화될수록 캐패시터 간 간섭 현상이나 전류 누설 현상이 심해진다. 이는 게이트 역시 마찬가지다.

이를 효과적으로 막을 수 있는 차세대 증착 재료를 개발해야 한다. D램 캐패시터의 경우 지금은 지르코늄계 재료가 쓰이지만, 차세대로는 지르코늄 외 다양한 물질이 후보군으로 올라와 있다. 이 증착 물질을 원자층 단위로 얹는 원자층증착기(ALD) 기술은 이미 국내 장비 업계가 세계적인 경쟁력을 갖고 있는 것으로 평가받고 있다.

모든 공정 사이사이에 쓰이는 세정 분야에서도 혁신이 필요하다. 기존 세정 장비는 웨이퍼를 고속 회전시키면서 세정 약액을 뿌리고 찌꺼기를 날려보냈다. 그러나 패턴 간격이 보다 좁아지고 단차가 커지면 기존 회전 방식을 사용했을 시 패턴이 휘거나 인접 패턴과 붙어버리는 문제가 발생한다. 업계 관계자는 “세정 분야에서도 또 다른 혁신이 필요하다”면서 “이미 삼성 등은 강한 압력과 높은 온도로 세정 공정을 수행하는 초임계 장비를 개발 완료해 재배치를 이뤘다”고 말했다.

10나노 미만으로의 회로 선폭 미세화가 단기 과제라면 중장기 기술 개발 과제로는 현재 P-N 접합 구조가 근간인 상보성금속산화막반도체(CMOS) 소자 구조와 실리콘 소재를 대체할 만한 신소재를 개발하는 것이 급선무라고 업계 전문가는 입을 모으고 있다.

김기남 삼성전자 반도체 총괄 사장은 “현재 CMOS 기술 방식으로 3~5나노까지 선폭을 축소할 수 있고 실리콘 재료 기준으로는 1.5나노까지 선폭 축소가 가능할 것으로 본다”고 말했다. 그 이후로는 CMOS가 아닌 새로운 소자 구조와 실리콘을 대체할 재료를 찾아야 한다는 의미다.

◇뇌 모방 반도체, 중장기 관점서 접근

회로 선폭 축소를 위한 전통의 장비, 재료, 공정 분야 혁신과 함께 4차 산업혁명을 이끄는 반도체 기술로 인공지능(AI) 분야가 빠질 수 없다. 현재 쓰이는 중앙처리장치(CPU), 그래픽처리장치(GPU)로는 기계학습 등 AI를 구현하기 위한 연산 성능이 크게 떨어진다. 전력 소모량 역시 높다.

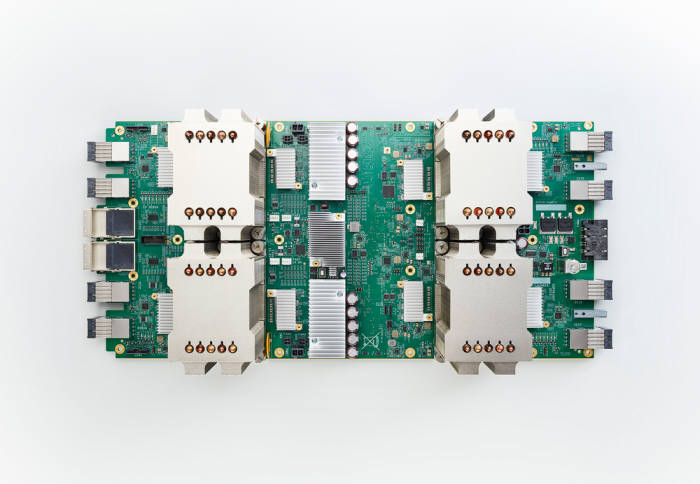

업계는 이를 해결하기 위해 사람 뇌를 닮은 뉴로모픽 아키텍처를 개발하고 있다. 마치 사람 뇌처럼 뉴런(신경세포)을 다량 집적하고 시냅스를 통해 여러 갈래로 연결하는 것이 기본 구조다. 구글은 이 같은 구조로 TPU(Tensor Processing Unit)를, IBM은 트루노스(Truenorth)라는 이름의 칩을 개발하고 고도화 중이다. 구글과 IBM은 클라우드 인프라 상에서 AI 연산을 처리한다는 목표를 세워뒀다.

반면에 퀄컴, 인텔, 하이실리콘, 마이크로소프트(MS) 등은 스마트폰과 가상현실(VR) 기기 등 완성품에 직접 탑재될 용도로 뉴로모픽 칩을 개발하거나 시스템온칩(SoC)에 내장하고 있다.

세계 각국의 AI 칩 개발 경쟁은 뜨겁다. 미국은 2014년부터 10년간 5조원 예산이 투입되는 브레인 이니셔티브 프로젝트를 추진 중이다. 이에 앞서 2008년부터는 국방고등연구계획국(DARPA)이 IBM과 함께 시냅스 프로젝트를 시작하며 뇌 모방 칩 개발에 박차를 가하고 있다. 유럽의 경우 2013년부터 26개국 135개 연구기관이 참여해 휴먼 브레인 프로젝트(HBP)를 실시 중이다. 기계학습이 가능한 칩과 컴퓨터 개발에 주력한다. 중국 역시 뇌 연구와 인공지능을 국책 과제로 실시 중이다. 이른바 차이나 브레인 프로젝트로 불린다.

유회준 KAIST 전기전자공학부 교수는 “한국이 정말 잘 할 수 있고 세계 시장에서도 우위를 점할 수 있는 반도체를 포함, 하드웨어 AI 분야를 집중 육성해야 한다”고 말했다.

한주엽 반도체 전문기자 powerusr@etnews.com