인텔이 대면적 인공지능(AI) 반도체 칩 제조가 가능한 첨단 패키징 기술을 선보인다. 반도체 파운드리(위탁생산) 역량을 강화, TSMC와 삼성전자에 밀린 파운드리 시장에 승부수를 던진 것으로 분석된다.

16일 업계에 따르면 인텔은 올해 AI 반도체 칩 패키징 기술을 대폭 업그레이드해 파운드리 역량을 강화한다. 지난해부터 관련 기술 로드맵을 수립하며 준비를 해왔다.

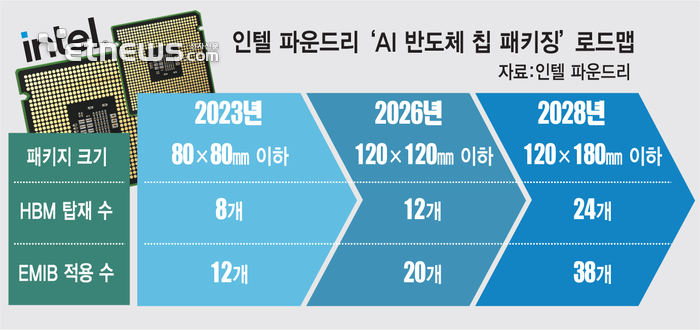

핵심은 '대면적' AI 반도체 패키징 기술이다. 구체적으로 120×120㎜ 크기 패키지를 공급한다. 현재 AI 반도체 칩 패키지는 크기가 대부분 100×100㎜다. 시장에 공급되는 엔비디아 최신 AI 반도체 칩 '블랙웰'도 이 크기를 채택하고 있다.

반도체 칩 패키지가 커지면 그래픽처리장치(GPU)·중앙처리장치(CPU) 등 연산 장치와 메모리를 더 많이 탑재할 수 있다. 특히 AI 메모리로 꼽히는 고대역폭메모리(HBM)를 배치할 자리가 넓어진다. 이를 통해 AI 반도체 칩 성능을 대폭 끌어올릴 수 있다.

다만, 패키지 크기를 키우면 휨 현상과 수율 저하 등 공정 난도가 높아진다. 패키지 확대를 위한 고도의 기술력이 필요한 이유다.

인텔은 120×120㎜ 패키지로 HBM을 최소 12개 이상 탑재할 예정이다. 100×100㎜ 크기의 경우 통상 HBM이 8개 탑재된다. 인텔은 여기에 그치지 않고 2028년에는 120×180㎜ 크기 패키지도 내놓을 계획이다. HBM을 24개까지 탑재할 공간을 확보한다는 구상이다.

인텔 파운드리 관계자는 “현재 시장에서는 120×120㎜ 이상의 AI 반도체 칩 패키지를 찾고 있다”며 “AI 확산을 고려하면 장기적으로 패키지 크기가 250×250㎜까지 커지게 될 것이며 여기에 맞춰 패키지 크기를 지속 확대할 것”이라고 밝혔다.

인텔 독자 패키징 기술인 'EMIB(Embedded Multi-die Interconnect Bridge)'도 파운드리 역량 강화의 핵심이다. EMIB는 반도체 기판에 내장된 실리콘 브릿지를 이용, 패키지 내 다른 반도체와 연결하는 기술이다.

인텔은 EMIB에 실리콘관통전극(TSV) 기술을 적용한 'EMIB-T'를 지난해 공개한 바 있다. 현재 메모리 제조사들이 양산 공급을 추진 중인 HBM4에 적합하도록 EMIB-T 구조를 준비 중인 것으로 전해진다. 새로운 구조는 AI 반도체 칩에 안정적인 전력을 공급하는 데 초점을 맞췄다.

인텔의 행보는 파운드리 시장에서 반전을 꾀하기 위한 전략이다. AI 확산에 따라 핵심 인프라인 AI 반도체 칩 위탁생산 수요가 커졌지만 인텔은 TSMC와 삼성전자보다 뒤처진 상황이다. 이 상황을 타개하기 위해 첨단 패키징 역량을 한층 강화하려는 시도다.

업계 관계자는 “인텔의 첨단 공정 기술은 대부분 자사 반도체 칩에 적용해왔지만 파운드리 사업 확대를 위해 외부 고객에도 적극적으로 문을 열 것”이라며 “다양한 패키지 크기와 패키징 기술로 고객 수요를 잡으려는 전략”이라고 말했다.

권동준 기자 djkwon@etnews.com