SK하이닉스가 M16에 8000억원 규모로 설비투자를 단행한다. M16은 지난 2월 준공된 SK의 최신 반도체 공장(팹)으로, 극자외선(EUV) 공정을 이용한 메모리 생산을 준비해 왔다. 차세대 메모리 양산에 속도를 내는 동시에 메모리 시황을 반영한 투자로 풀이된다.

SK하이닉스는 올 하반기 M16에 12인치 웨이퍼 투입량 기준 월 1만8000장(18K) 규모의 설비를 갖출 계획이다. 3분기 8000장(8K), 4분기 1만장(10K)을 각각 투자하고 국내외 장비 협력사와 세부 일정 등을 협의한 것으로 알려졌다. 금액으로는 약 8000억원에 이르는 규모다. 이 사안에 밝은 업계 관계자는 “SK하이닉스가 하반기 M16에 18K 규모를 투자할 방침”이라면서 “장비 구매를 협의하고 있는 것으로 안다”고 전했다.

투자는 2022년 계획한 투자분 가운데 일부를 앞당겨 집행하는 것이다. SK하이닉스는 지난 4월의 1분기 실적 발표 콘퍼런스콜에서 “반도체 전반에 걸친 공급 부족에 대응하기 위해 내년으로 계획된 시설투자 일부를 올해 하반기로 앞당겨 집행할 계획”이라고 밝힌 바 있다. 규모와 시기 등 세부 투자 내용이 확인된 건 처음이다.

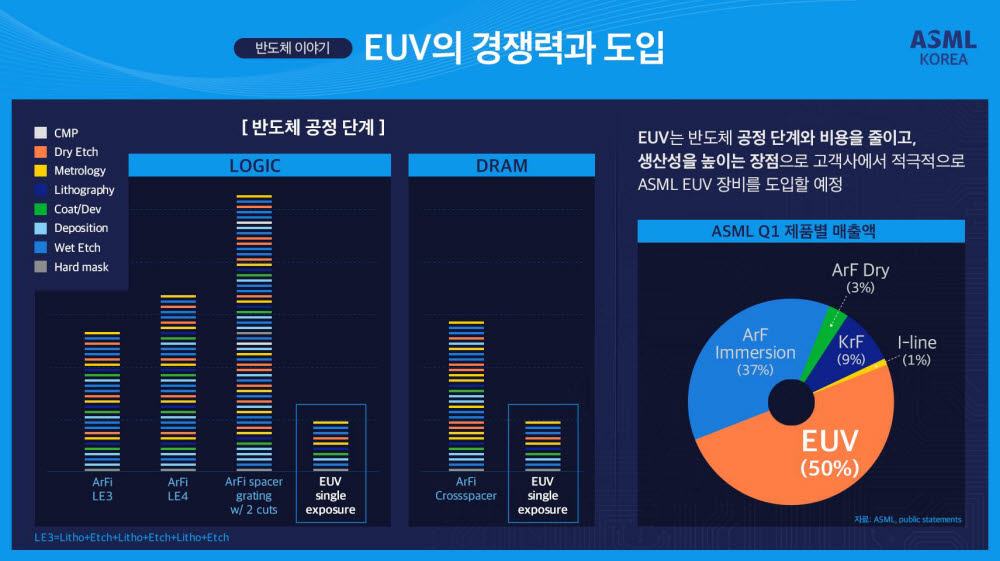

경기도 이천에 위치한 M16은 2018년 11월 착공 이후 총 3조5000억원, 연인원 334만명을 투입해 25개월 만에 준공한 SK하이닉스의 최신 팹이다. SK하이닉스 최초의 EUV 노광기가 도입됐다. EUV는 반도체 포토 공정에서 EUV 파장 광원을 사용하는 것으로, 기존 불화아르곤(ArF)보다 파장 길이가 짧아(14분의 1 미만) 반도체에 미세 회로 패턴 구현 때 유리하고 성능과 생산성도 높일 수 있다.

SK하이닉스는 EUV 기반 메모리 양산과 수요가 늘고 있는 D램 메모리 시장을 대비해 하반기 투자를 준비하는 것으로 분석된다. M16에는 상반기 EUV 노광기 1대와 월 1만장(10K) 규모의 메모리 설비가 채워진 것으로 알려졌다. 1만장은 반도체 팹이 세워졌을 때 처음 갖춰 놓는 초도(파일럿) 라인 수준으로, SK하이닉스는 EUV 기반 메모리 양산을 위해 하반기에 18K를 추가하는 것으로 해석된다.

SK하이닉스는 하반기 '4세대 10나노급'(1a) D램 생산을 목표로 준비해 왔다. 1a D램은 이제 막 도입된 최신 공정에 생산하는 첫 제품인 만큼 수율 등 안정화에 시간이 소요될 것으로 예상된다.

설비투자는 최근 D램 시황도 고려됐다. 시장조사업체 트렌드포스에 따르면 3분기 D램 고정거래가격은 2분기 대비 3~8% 상승이 예상된다. D램 고정가는 올해 들어 지속 강세를 보이며 상반기에 20%대 상승폭을 보였으며, 하반기도 긍정적일 것으로 전망된다.

SK하이닉스가 EUV 팹 투자에 나서면서 EUV D램 양산 경쟁에도 관심이 쏠리고 있다. 삼성전자와 SK하이닉스는 나란히 올 하반기를 1a D램 양산 목표 시점으로 잡았다. D램 시장 1, 2위인 삼성과 SK의 차세대 메모리 양산 경쟁이 불이 붙을지 주목된다. 메모리 업계 3위인 마이크론은 EUV 공정 도입이 상대적으로 늦어 연구개발(R&D) 단계에 있다. EUV 공정은 노광기 1대가 1500억원에 이를 정도로 막대한 자금이 소요되고, 공정 기술도 까다로워 반도체 업체의 기술경쟁력을 가르는 기준이 되고 있다.

윤건일기자 benyun@etnews.com, 권동준기자 djkwon@etnews.com