어플라이드머티어리얼즈가 초미세 공정의 금속 배선 시 전기 저항을 크게 줄여주는 '아이오닉 PVD 시스템'을 8일 공개했다.

첨단 공정으로 회로 선폭이 얇아질수록 금속 배선 전기 저항은 대폭 증가한다. 이는 반도체 칩 성능을 저하하고 전력 소비를 높이는 원인이 된다.

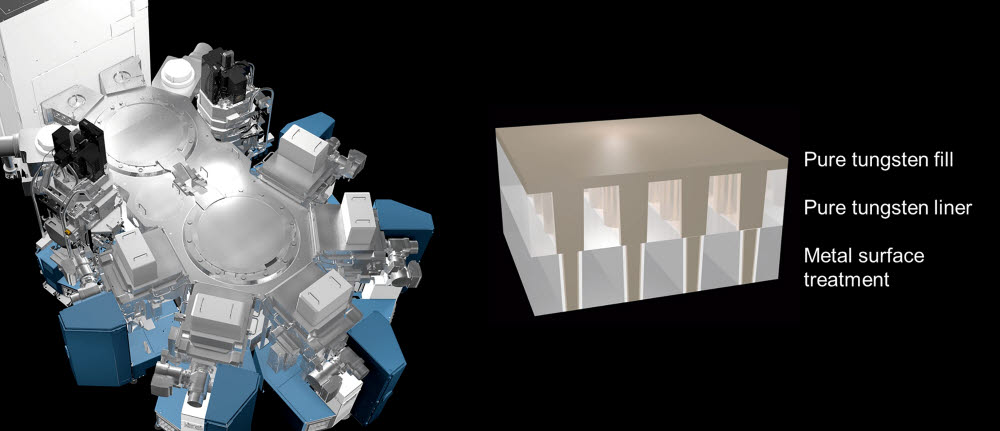

어플라이드 아이오닉 PVD 시스템은 고진공 시스템에서 물리기상증착(PVD)과 화학기상증착(CVD) 공정을 지원한다. 표면 처리 공정도 처리할 수 있다. 반도체 제조 시 질화 티타늄 소재로 만들어지는 고저항 라이너와 장벽층을 100% 순도 저저항 PVD 텅스텐 박막으로 대체한다. CVD 텅스텐과 결합시켜 100% 순도 텅스텐 메탈 전극을 생성할 수 있다. 전기 저항을 줄여주고 3나노미터 이하 미세 공정을 구현할 수 있다.

프라부 라자 어플라이드머티어리얼즈 반도체 프로덕트 그룹 부사장 겸 총괄 매니저는 “전기 저항을 해결하는 어플라이드의 최신 혁신은 재료 공학이 지속적인 2D 미세공정화를 어떻게 실현하는지 보여주는 좋은 사례”라며 “혁신적인 아이오닉 PVD 시스템은 트랜지스터 성능을 떨어뜨리는 병목 현상을 제거해 트랜지스터 운용 속도를 높이고 전력 손실을 줄여준다”고 밝혔다.

권동준기자 djkwon@etnews.com