생성형 인공지능(AI) 기업 오픈AI가 자사 반도체 패키징 특허를 처음 공개했다. 연산 칩 주변에 배치할 수 있는 고대역폭메모리(HBM) 수량을 기존보다 최대 5배 가까이 늘릴 수 있는 설계 기술을 구체화했다.

업계에 따르면 오픈AI는 '내장형 논리 브리지를 통한 고대역폭 메모리 칩렛, I/O 칩렛 및 컴퓨팅 칩렛의 비인접 연결' 특허를 이달 공개했다.

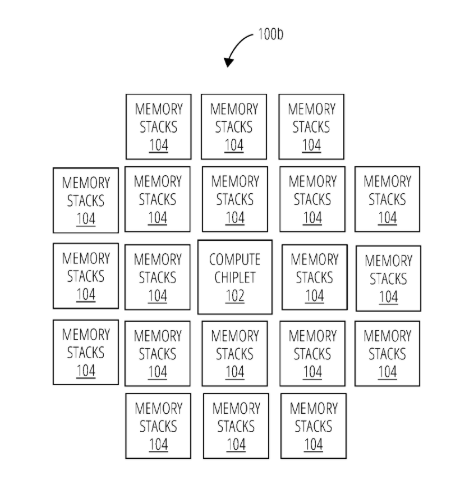

해당 특허 도면을 살펴보면 가운데 칩렛을 HBM이 시루떡(Rice cake)처럼 빽빽하게 이중, 삼중으로 둘러싸고 있다. 이는 반도체 패키징의 오랜 난제인 '해안선 제한(Shoreline Limit)'을 극복하기 위한 목적이다.

현재 AI 칩은 연산 칩(GPU 등)의 사방 둘레에 HBM을 배치한다. 하지만 국제 표준(JEDEC)이 신호 감쇠 방지를 위해 연결 거리를 6mm 이내로 제한하다 보니, 칩의 물리적 둘레(해안선)에 붙일 수 있는 HBM 스택은 4~8개 수준에 머물러 왔다.

오픈AI는 브리지(Bridge) 내부에 능동 회로를 삽입한 '임베디드 로직 브리지' 개념을 도입했다. 이를 통해 통신 거리를 최대 16mm까지 확장, 연산 칩과 직접 맞닿지 않은 '2열', '3열' 위치의 원거리 HBM까지 초고속으로 연결하는 구조를 제안했다.

이 기술이 상용화되면 하나의 컴퓨팅 칩렛에 최대 20개의 HBM 스택을 연결할 수 있게 된다. 이는 현재 엔비디아의 블랙웰(8개) 시리즈를 한참 상회하는 수준이다.

업계 전문가들은 이번 특허가 인텔의 2.5D 패키징 기술인 'EMIB(Embedded Multi-Die Interconnect Bridge)'와 구조적으로 유사하다는 점에 주목했다.

EMIB는 고가의 실리콘 인터포저 대신 필요한 부분에만 브리지를 삽입해 비용을 낮추고 설계를 유연하게 하는 기술이다. 오픈AI의 기술은 여기에 '로직(Logic)' 기능을 추가해 성능을 극대화한 형태다. 향후 오픈AI가 설계하고 인텔 파운드리가 제조하는 '커스텀 AI 칩' 탄생의 가교가 될 가능성이 제기된다.

업계 관계자는 “창의적인 설계지만 아직 특허 단계라 실제 성능 개선 효과에 대해서는 단정하기 어렵다”며 “HBM 탑재가 늘어나는 구조의 특성 상 발열(Thermal) 을 잡아내는 것이 향후 주된 과제로 보인다”고 설명했다.

업계에서는 이번 특허가 오픈AI가 단순 서비스 기업을 넘어 자체 칩(Custom Silicon) 설계 역량을 확보했다는 신호탄으로 해석했다. 오픈AI를 포함한 주요 AI 기업들은 최근 엔비디아 의존도를 줄이기 위해 독자 칩 설계 역량을 강화하고 있다. 단순 AI 모델 개발사를 넘어 자사 워크로드에 최적화된 하드웨어 토대를 구축하는 게 목적이다.

이형두 기자 dudu@etnews.com