온디바이스 인공지능(AI) 시대 임박을 계기로 차세대 저전력 메모리 개발을 가속하기 위해 산업계와 학계가 손을 잡았다.

9일 업계에 따르면 국내 시스템 반도체 기업 코싸인온이 인하대학교와 차세대 모바일 메모리 규격인 'LPDDR6(Low Power Double Data Rate 6)' 인터페이스 IP(설계자산) 개발을 위한 공동 연구에 착수한다.

이번 연구는 온디바이스 AI 시장 확대에 따른 메모리 병목 현상을 해결하고, 해외 기업이 주도해 온 인터페이스 IP 기술을 국산화하는 게 목적이다. 코싸인온과 인하대 연구진은 LPDDR6 규격에 최적화된 컨트롤러와 피(PHY, 물리계층) IP를 공동 설계한다.

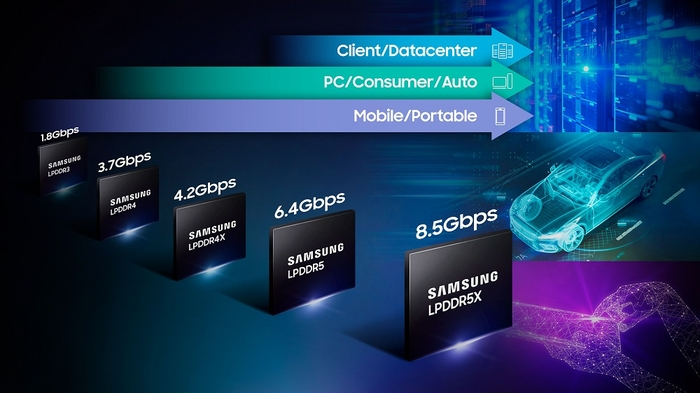

LPDDR6는 기존 LPDDR5X 대비 데이터 전송 속도가 10.6Gbps 이상으로 향상된 규격이다. 지난해 7월 표준이 제정됐다. 기존 세대보다 약 50% 이상 성능 향상과 20% 이상 전력 효율 개선을 목표로 한다. 기존 16비트 채널 구조에서 벗어나 12비트 서브채널 2개를 묶어 24비트를 구성했다. 만약 4채널 패키지 구성 시 총 96비트 폭을 제공해 대역폭을 LPDDR5X 대비 두 배 가까이 높일 수 있다.

이는 기기 내에서 직접 구동되는 거대언어모델(LLM) 환경에 최적화된 설계다. LLM은 수십억개 파라미터를 실시간으로 읽어와야 하는데, 이 데이터가 오고가는 도로를 대폭 늘려 메모리 병목 현상을 완화하려는 목적이다.

현재 메모리 인터페이스 IP 시장은 시놉시스(Synopsys), 케이던스(Cadence) 등 글로벌 기업들이 주도하고 있다. 이노실리콘 등 중국 기업들도 2026년 상용화를 목표로 LPDDR6 IP 개발에 가속도를 내며 한국 기업과의 기술 격차를 좁히고 있다. 한국에서는 삼성전자와 SK하이닉스가 국제고체회로학회 등에서 자사 LPDDR6 개발 성과를 공개한 바 있다. 코싸인온-인하대의 이번 공동 연구가 성공할 경우 국산 IP 점유율 확대는 물론, 국내 팹리스 기업들의 개발 비용 절감과 기술 자립도 향상에 기여할 것으로 전망된다.

코싸인온은 고성능 AI 및 시스템 반도체 설계 기술을 보유한 국내 팹리스 기업이다. 초미세 공정 기반의 고속 인터페이스 IP와 저전력 설계 분야에서 기술력을 쌓아왔다. 인하대학교는 산업통상자원부의 반도체 특성화 대학 지원사업 등을 통해 반도체 설계 및 공정 분야의 전문 인력을 양성하고 있으며, 산학협력을 통한 차세대 반도체 원천 기술 확보에 주력하고 있다.

이형두 기자 dudu@etnews.com